컴퓨터공학 공부 다시 시작하기 12주차 - 데드락과 스타베이션 개념 이해, 가상 메모리 개념 이해, 페이징 시스템 개념 이해

1. 데드락과 스타베이션 개념 이해

데드락(Deadlock, 교착상태)

- 무한 대기 상태: 두 개 이상의 작업이 서로 상대방 작업이 끝나기만 기다리고 있어 다음 단계로 진행하지 못함

(여러 프로세스가 동일 자원 점유)

- 배치 처리 시스템에서는 일어나지 않는 문제

- 프로세스, 스레드 둘다 이와 같은 상태가 일어날 수 있음

- 휴대폰에서 특정 앱이 실행 중 동작이 안될 때 이유 중 하나

-> 이를 디버깅하기 위해 데드락에 대한 이해가 필요하며, 운영체제는 앱이 일정 시간 반응이 없으면 강제 종료시킴

스타베이션(Starvation, 기아상태)

- 특정 프로세스의 우선순위가 낮아, 원하는 자원을 계속 할당 받지 못하는 상태

- 여러 프로세스가 부족한 자원을 점유하기 위해 경쟁할 때, 특정 프로세스가 영원히 자원 할당을 못 받는 경우

- 해결 방안: 프로세스 우선순위를 수시로 변경(오래 기다린 프로세스의 우선순위를 높게)

-> 또는 요청 순서대로 처리하는 FIFO(선입선출) 기반 요청큐 사용

2. 가상 메모리 개념 이해

- 프로세스마다 충분한 메모리를 할당하기엔, 실제 메모리 크기에 한계가 있기에 필요

=> 리눅스는 한 프로세스가 4GB이며, 통상 메모리는 8GB/16GB 정도

- 한 프로세스만 실행 가능한 시스템(배치 처리 시스템 등)

: 프로그램을 메모리로 로드(load) > 프로세스 실행 > 프로세스 종료(메모리 해제)

=> 여러 프로세스를 동시에 실행하는 시스템의 경우,

메모리 용량이 부족할 뿐만 아니라 프로세스 메모리 영역 간 침범이 있을 수 있음

가상 메모리(Virtual Memory System)

- 메모리가 실제 메모리보다 많아 보이게 하는 기술

- 프로세스 간 공간을 분리하여, 프로세스 이슈가 전체 시스템에 영향을 주지 않을 수 있음

- 프로세스는 가상 주소(프로세스가 참조하는 주소)를 사용하고,

실제 해당 주소에서 데이터를 읽고 쓸 때만 물리 주소(실제 메모리 주소)로 바꿔줌

- MMU(Memory Management Unit)

: CPU에서 코드 실행 시 가상 주소 메모리에 접근할 때, 해당 주소를 물리 주소값으로 변환해주는 하드웨어 장치

=> 하드웨어 장치를 이용해야 주소 변환이 빠르기에 별도 장치를 두는 것

- 메인 메모리에 실제 각 프로세스의 데이터가 조각으로 씌여 있음

3. 페이징 시스템 개념 이해

페이징 시스템(Paging System)

- 가상 주소 공간과 이에 매칭하는 물리 주소 공간을 크기가 동일한 페이지로 관리하는 것

- 하드웨어 지원이 필요함(예시: Intel x86 시스템[32비트]에서는 4KB, 2MB, 1GB 지원, 리눅스에서는 4KB 지원)

- 페이지 번호를 기반으로 가상 주소-물리 주소 매핑 정보를 기록하고 사용함

페이징 시스템 구조

- page 또는 page frame: 고정된 크기의 block(4KB)

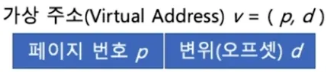

- 가상 주소 v = (p, d) [p: 가상 메모리 페이지, d: p안에서 참조하는 위치]

=> 페이지 크기가 4KB일 경우, 가상 주소의 0~11비트가 변위(d)를 나타내며 12비트 이상이 페이지 번호가 될 수 있음

페이지 테이블(Page Table)

- 물리 주소에 있는 페이지 번호와 해당 페이지의 첫 물리 주소 정보를 매핑한 표

- 가상 주소 v = (p, d) [p: 페이지 번호, d: 페이지 처음부터 얼마 떨어진 위치인지]

=> 특정 가상 주소에 엑세스하려면, 페이지 테이블에 해당 가상 주소가 포함된 page 번호가 있는지 확인한 후,

이 페이지가 매핑된 첫 물리 주소를 알아내고(p') p'+d가 실제 물리 주소가 됨

페이징 테이블과 MMU(컴퓨터 구조)

프로세스 생성 시 페이지 테이블 정보도 생성되면,

PCB 등에서 해당 페이지 테이블에 접근이 가능하며 정보는 물리 메모리에 적재됨

-> 프로세스 구동 시 해당 페이지 테이블의 base 주소가 별도 레지스터(CR3)에 저장되며,

CPU가 가상 주소에 접근할 때 MMU가 페이지 테이블 base 주소에 접근하여 물리 주소를 가져오는 것

**다중 단계 페이징 시스템?

미리 페이징 정보를 만들어놓지 않고 특정 페이징 주소 영역(디렉토리)에 대해서만 만들어둠

-> 즉, 페이징 정보를 단계를 나누어 생성함(필요 없는 페이지를 생성하지 않으면 공간 절약 가능)

=> 페이지 번호를 나타내는 bit를 구분해서 단계를 나눔