1. 16비트 가산기와 클럭 동작 이해

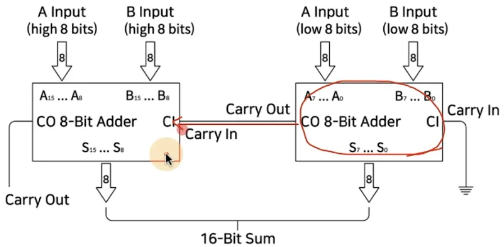

여러 자리 계산이 가능한 전가산기

8비트 전가산기 - 8개를 연결해서 조합

16비트 전가산기 - 2의 16승(65536)까지 덧셈 가능

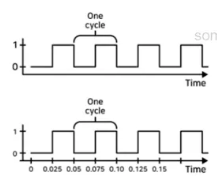

*Oscillator(클럭을 만들 수 있음)

- Input이 0이면 Output은 1, 하지만 Output 1은 다시 Input 0으로..

-> Output 값은 0과 1을 반복할 것

- Cycle: a interval(주기: 한 사이클에 필요한 시간)

- frequency(단위-hertz): 주기/1 (cycle/sec)

-> 아래 예제는 frequency가 20 hertz(Hz)

2. 플립플롭과 메모리 동작 이해

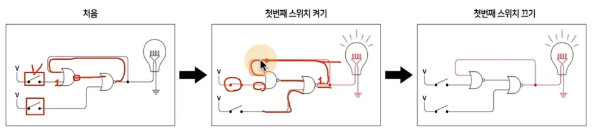

플립플롭 이란?

- flip-flop: 데이터를 저장하는 조합논리회로

- 첫 번째 스위치를 키면 불이 켜지는데, 스위치를 끄면 불이 켜진채로 지속됨

- 두 번째 스위치를 끄면 불이 꺼지는데, 스위치를 켜도 불은 꺼진채로 지속됨

- 스위치를 키고 끄고를 저장 가능!

-> 불이 켜져 있다: 최근에 첫 번째 스위치가 켜졌었다.

-> 불이 꺼져 있다: 최근에 두 번째 스위치가 꺼졌었다.

NOR 게이트 조합

첫번째 스위치를 킨 후 끄면

두번째 스위치를 끈 후 켜면

RS 플립플롭

- R-S(Reset-Set) flip-flop

-> Q는 output, Q위에 바(-)가 있으면 Q의 반대값

-> 단, S와 R이 1인 상태는 피하도록 설계(Q값과 Q바의 값이 둘 다 0이 되기 때문)

Level-triggered flip-flop

Hold That Bit이라는 이름으로 조합논리회로 추가

- Hold That Bit이 1일 때만, Data가 1일 때 출력값에 적용됨

D-type flip-flop

- R/S(두 input)를 Data(하나의 input)으로 변경

-> R/S 둘 다 1일 경우는 피하며, R/S 둘다 0일 경우도 Q값에 영향을 안 주므로 피함

Level-triggered D-type flip-flop

- D는 Data를 의미

- Level-triggered에서는 Hold That Bit이 1일 때만 Data 값을 저장한다는 의미

- RS 플립플롭에서 R/S 둘 다 1, 0인 경우를 피하도록 설계한 조합논리회로

3. 8 x 1 메모리 동작과 구성 이해

1 bit latch

Level-triggered D-type filp-flop

- Hold That Bit를 Write로 표시

- Data In이 데이터를 넣을 때 Write도 1이 되어야 함

- 1 bit를 일시적으로 저장할 수 있는 메모리

8 bit latch

- Write이 1일 때 8 bit Data Inputs이 8 bit Data Outputs에 저장됨

- Write이 0이면 8 bit Data Outputs 값이 유지됨

8-to-1 Selector

- 8 bit 데이터에서 특정 bit 값만 출력하기

- 하나의 백열전구로 8개 각 비트의 값을 알려면?

-> 3개 스위치로 8개 비트 구분 가능: 000, 001, 010, 011, 100, 101, 110, 111

- 8개의 1 bit latch 중에서 하나의 데이터 출력 신호 선택 가능

3-to-8 decoder

- 8개의 출력 중, V 스위치로 단 하나의 출력 이외에는 0

- Write가 1, V 스위치로 특정 출력 선정, Data In의 값이 특정 latch에 쓰여짐

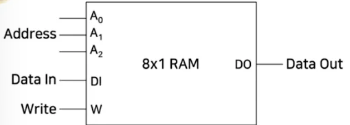

온전한 8 bit latch 회로 RAM(Random Access Memory)

- 3-to-8 decoder와 8-to-1 selector로 구성(이게 바로 주소=Address)

- S0, S1, S2가 decoder와 selector에 동일하게 적용(데이터 읽고 쓸 수 있는 Address)

- Write가 1이면, Address에 Data In 값이 씌여짐

- Data Out은 항상 Address에 해당하는 값을 출력

- 3 Address가 있으면 8개 중 하나의 비트를 선택해서 쓰거나 읽을 수 있음

8 x 1 RAM: 8개 비트 중 1개의 특정 비트를 쓰고 읽을 수 있는 메모리

- Memory: 데이터 저장 가능

- Read/Write: 특정 공간에 새로운 데이터 저장/읽기 가능

- Random Access: Address 지정을 통해 특정 공간 값 접근 가능(어떤 메모리는 순차 접근만 가능함)